# T-TC Time Error

Testing Transparent Clocks as per ITU-T G.8273.3 using Paragon-X

- Noise Generation

- Noise Tolerance

- Noise Transfer

- Transient Response

- Holdover Performance

The accuracy of Telecom Transparent Clocks (T-TCs) is essential to the successful roll-out of LTE-A and TDD-LTE. To meet the new G.8273.3 compliance limits, T-TCs must meet a very stringent constant Time Error (cTE) limit of 20 or 50 nanoseconds depending on device class. This ensures that the maximum number of nodes can be deployed within the network's Time-Error budget.

This Test Guide shows how the Calnex Paragon-X can be used to prove T-TC compliance to G.8273.3 and provides procedures to measure noise generation, time noise tolerance and transfer, packet layer transient response and holdover performance.

# **Contents**

| Hardware and Software Required3                                                  |                                                  |

|----------------------------------------------------------------------------------|--------------------------------------------------|

| Connecting Paragon-X to T-TC (Device under Test)4                                |                                                  |

| Setting up the Paragon-X for G.8273.3 Conformance Tests5                         |                                                  |

| 3.1 Connection to Paragon-X from GUI                                             | 5                                                |

| Selection of 1588 Operating Mode and Master/Slave Mode                           | 5                                                |

| Noise Generation – G.8273.3 Section 7.19                                         |                                                  |

| Time Noise Tolerance – G.8273.3 Section 7.216                                    |                                                  |

| Time Noise Transfer – G.8273.3 Clause 7.3                                        |                                                  |

| Packet Layer Transient Response and Holdover Performance – G.8273.3 Clause 7.419 |                                                  |

| pendix 1 – Tests for a G.8273.3 T-TC20                                           |                                                  |

| (1)                                                                              | Connecting Paragon-X to T-TC (Device under Test) |

# 1. Hardware and Software Required

### Paragon-X

| Option 110 | 1GbE interface support                                                             |

|------------|------------------------------------------------------------------------------------|

| Option 111 | 10GbE interface support (if DUT has 10G interface)                                 |

| Option 201 | Advanced IEEE1588v2 features                                                       |

| Option 205 | Wander measurement                                                                 |

| Option 206 | Phase and time measurement                                                         |

| Option 213 | SyncE wander and ESMC (if DUT uses SyncE)                                          |

| Option 250 | IEEE 1588v2 One-box T-BC, T-TC and OC Test                                         |

| Option 133 | External 1pps/ToD/Frequency Converter accessory (if required to match DUT outputs) |

#### **Software versions:**

- Paragon-X: X.10.35.xx and later

- Calnex Analysis Tool (CAT): v18.xx and later

Note: Calnex recommends checking the Calnex website for access to the latest software release versions.

#### **Accessories**

- SFP or SFP+ devices as required1

- Cables as required

- Calnex BNC/RJ-45 adapter cable (required for 1pps accuracy/time error measurement)

#### **Frequency Reference Source**

Option 132 Rubidium Interface (optional)

#### **Document References**

- Recommendation ITU-T G.8273.3 Timing Characteristics of Telecom Transparent Clocks

- IEEE Std 1588TM -2008 IEEE Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems

- Tech Note Cabling Considerations Document [CX5009]

<sup>&</sup>lt;sup>1</sup> XFP devices are not recommended for Time Error measurements as the retiming that is an integral element of the XFP introduces significant uncertainty when performing a Time Error test

# 2. Connecting Paragon-X to T-TC (Device under Test)

**Front Panel**

- 100MbE Electrical or Optical (SGMII SFP)

- 1GbE Electrical or Optical (SFP) with option 110 fitted

- 10GbE Optical (XFP or SFP+) with option 111 fitted

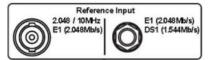

#### **Rear Panel**

The Paragon-X accepts the following reference clocks which should be applied to one of the reference inputs on the rear panel of the Paragon-X:

- 2.048/10MHz

- E1 (2.048Mb/s)

- DS1 (T1) (1.544Mb/s)

#### **Connections**

- 1. Connect Port 1 (Master side of Paragon-X) to the T-TC Master side.

- 2. Connect Port 2 (Slave side of Paragon-X) to the T-TC Slave side.

- 3. Connect the external reference, e.g. 10MHz, to the Paragon-X Reference Input.

# 3. Setting up the Paragon-X for G.8273.3 Conformance Tests

The following steps are required to set up the Paragon-X prior to performing the G.8273.3 Conformance tests:

- 3.1. Connection to Paragon-X from GUI

- 3.2. Selection of 1588 Operating Mode and Master/Slave Emulation

- 3.3. Configuration of physical connections

- 3.4. Measurement configuration

- 3.5. Preparing Master/Slave Emulation operation

- 3.6. Confirm PTP traffic on interfaces

- 3.7. Filtering capture traffic

- 3.8. Start of Master/Slave Emulation ready for test

#### 3.1 Connection to Paragon-X from GUI

- 1. Verify the physical connections have been completed as described in Section 2.

- 2. Start the Paragon-X GUI.

- 3. Select Start Up and Connect.

- 4. Enter the IP address of the Paragon-X (displayed on Paragon-X status display).

#### 3.2 Selection of 1588 Operating Mode and Master/Slave Mode

Select Operating Mode and enable 1588v2 and Master/Slave Emulation.

#### 3.3 Configuration of physical connections

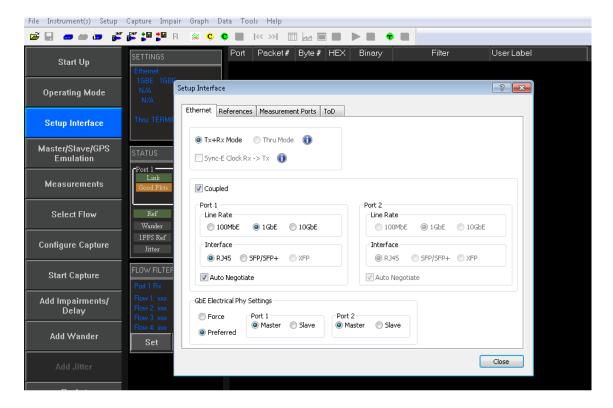

Select **Setup Interface** then **Line Rate** to match the T-TC under test.

#### 3.4 Preparing for Master/Slave Emulation

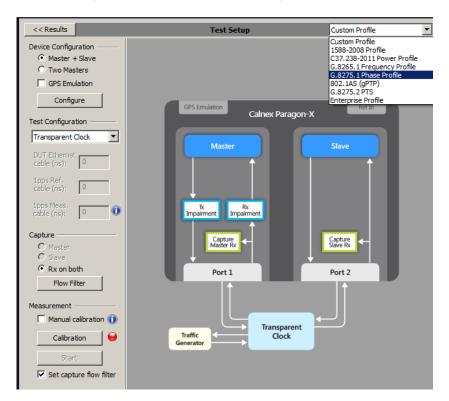

It is assumed that a G.8275.1 profile will be used in testing to the G.8273.3 standard and as a result testing will be carried out using L2 encapsulation in Multicast mode. The Master/Slave Emulation can be configured to use other profiles, e.g. using Unicast UDP/IPV4 etc., however, it should be noted that these profiles will not conform to the G.8273.3 standard.

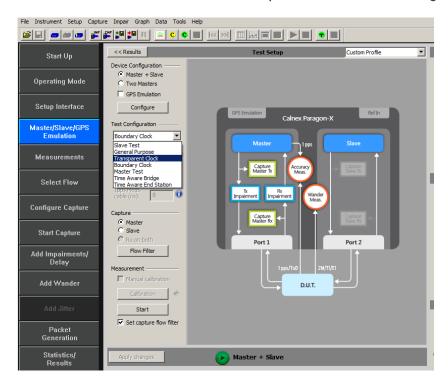

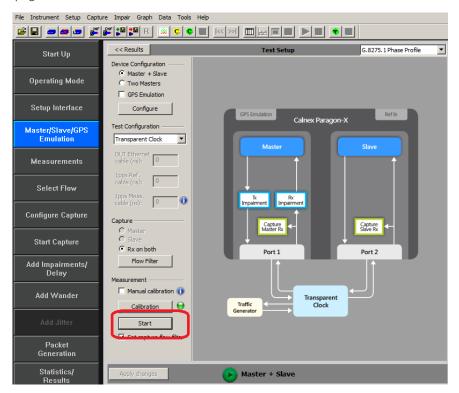

1. Select *Master/Slave Emulation* then select *Transparent Clock* in the *Test Configuration* drop down menu.

2. Select **G.8275.1** profile from the **Custom Profile** drop down menu.

#### Calibration

#### **Auto-calibration**

By default, the Paragon-X uses the same interface types on both sides of the T-TC. If this is the case then the end-toend delays from the Paragon-X Master to the Paragon-X Slave including the cable delays can be factored out of the measurements by carrying out an auto-calibration step.

To do this you must connect the cables to be used in the test together using a passive connector so that there is a complete path from the Paragon-X Master to the Paragon-X Slave. When this is done, press the Calibration button.

This will carry out a measurement that will calibrate the delays. When complete the LED which change to green.

#### Manual calibration

If the test set up has different interface types on each port (e.g. 1Gb Electric and 1Gb Optical) then auto-calibration cannot be performed. In this case the cable delays must be entered manually for the cables on either side of the T-TC connected to the Paragon-X.

Select Manual calibration and enter the DUT to Paragon-X cable delay. Values of 5.1 ns per 1 metre of electrical cable and 4.9 ns per 1 metre of optical cable can be expected. Only full nanosecond values are counted, so calculated values need to be rounded up or down to the nearest full nanosecond value.

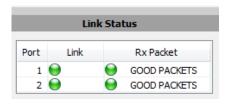

#### 3.5. Confirm PTP traffic on interfaces

1. Check the link to make sure that the PTP packets are running without error. If working successfully both Link and Packet status should show green status.

2. Stop Master/Slave Emulation in order to configure capture characteristics and to enable impairment operation.

### 3.6. Filtering capture and impairment traffic

The tests detailed in Sections 4 to 7 of this document are dependent on the generation, capture and impairment of the 1588 messages associated with T-TC phase and sync performance. It is therefore necessary to ensure that the correct messages are handled by the Paragon-X in Master/Slave Emulation mode. This is achieved by defining a set of traffic filters which will determine the messages that are captured and impaired.

By default, the capture filters are automatically enabled for the Transparent Clock test when the Start button is pressed in the *Master/Slave Emulation* Test Configuration window.

### 4. Noise Generation - G.8273.3 Section 7.1

#### **Test Description**

The noise generation of a T-TC represents the amount of noise produced at the output of the T-TC when there is an ideal input reference packet timing signal and, if the T-TC is supporting physical layer frequency reference, an ideal physical layer reference. The noise generation has two components, the constant time error (cTE) and the time noise generation (MaxITEI, dTE).

#### **Measurement Process**

The standard specifies that the test should be carried out with both PTP and SyncE active.

Note: The Master/Slave Emulation Configuration steps described in Section 3 must be performed prior to this test. Impairments are not required for this test.

#### **4.1.Test Procedure**

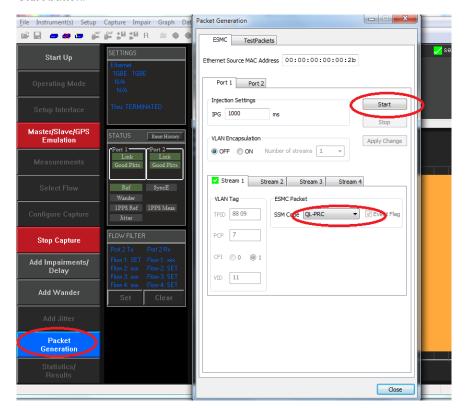

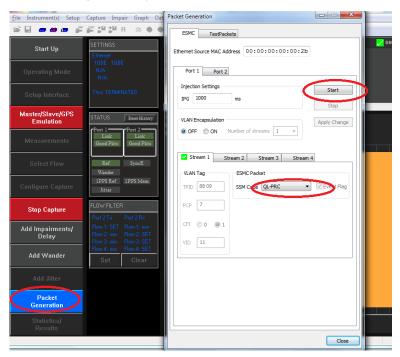

1. To enable SyncE, select Packet Generation with SSM code of QL\_PRC. To start ESMC generation click on the Start button.

2. With Master/Slave Emulation mode running, start a capture using the Start button in the Master/Slave Test Setup

- 3. Allow the capture to run for at least 2000s. Then use the Stop Capture button to stop the capture.

- 4. Measurements: Time Error results can either be viewed during capture or after capture has been stopped.

#### **Time Error Results (Constant Time Error)**

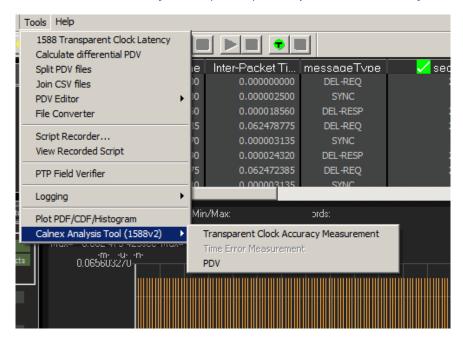

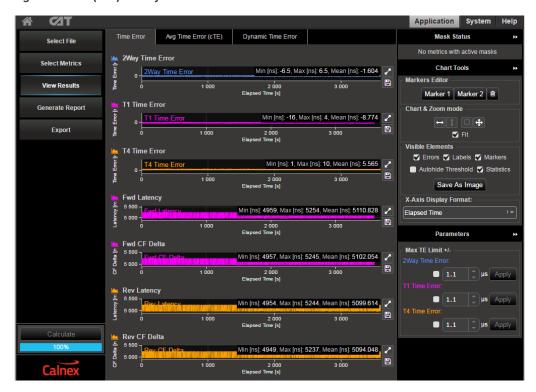

1. Select Tools > Calnex Analysis Tool (1588v2) > Transparent Clock Accuracy Measurement.

The Calnex Analysis Tool will launch and display the Time Error metrics tab. This will include the metrics Time Error, Avg Time Error (cTE) and Dynamic Time Error.

The key measurement for T-TC Time Error is the 2Way Time Error result for the above metrics. Focus should be placed on the analysis of this result.

T1 and T4 results are useful in the case where further analysis is required investigate issues raised by the 2Way result values.

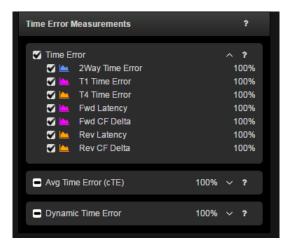

Note: The complete set of metrics can be viewed by expanding the appropriate list in the Measurement Analysis block by clicking on the + symbol against each metric.

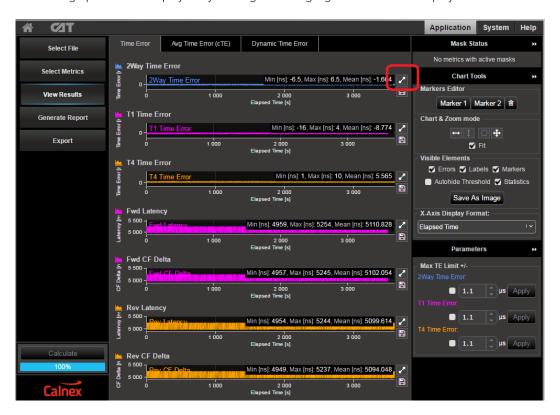

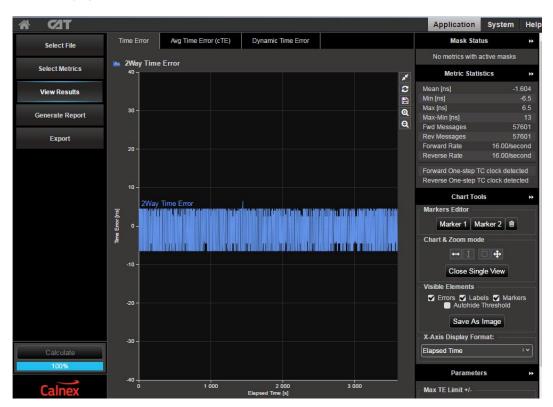

Individual graphs can be displayed by clicking on the highlighted area in the display below.

This will display:

To return to the multi graph display click on the same icon in the single graph display.

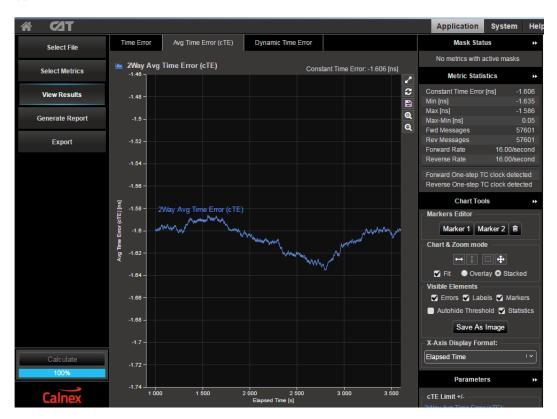

2. Select the Avg Time Error (cTE) metric tab and this will show the 2Way Avg Time Error (cTE) graph. This is a measure of the timing being delivered by the egress 1588 PTP flow and is the best view of the core data. The Constant Time Error value will be displayed. This result can expose the underlying phase movement, significant to the slave.

#### **G.8273.3** refers to Constant Time Error stating:

"Note: Constant time error and the method to estimate are defined in G.8260. For the purpose of testing the limits in Table 1, an estimate of constant time error should be obtained by averaging the time error sequence over 1000s."

To cater for this definition, the Constant Time Error displayed is a result of a moving average of 1000s being applied to the raw Time Error results.

3. Check your result conforms to the G.8273.3 spec [1.4.1].

There are two classes of device:

- Class A for devices which conform to ±50ns cTE

- Class B for devices which conform to ±20ns cTE

Check with the vendor which class of device is being tested.

### Further Analysis (Optional)

- Although not part of the standard test, further analysis can be provided by repeating the test for T1 and T4 constant Time Error to inspect for patterns and/or offsets.

- For further analysis, select the *Time Error* tab for unfiltered Time Error results i.e. *2Way Time Error*, *T1 Time Error* (forward) and T4 Time Error (reverse) to further characterise the T-TC. These raw Time Error results containing both Constant and Dynamic Time Error may be useful as a troubleshooting aid.

### **Time Error Results (Dynamic Time Error)**

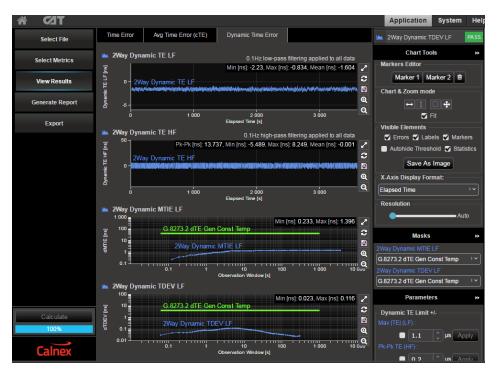

4. Select the *Dynamic Time Error* tab to display the *filtered* Time Error results. This will display the Dynamic Time Error results as Low Frequency measurements and High Frequency measurements.

Note that these results are filtered at 0.1Hz.

- 5. Compare the results against the ITU-T limits by loading the *G.8237.2 dTE Gen Const Temp* masks.

- 6. Check for PASS/FAIL versus masks. If the masks pass then the status in the Mask Status Block will indicate PASS Mask failure will be indicated by FAIL

# Time Error Results (MaxITEI)

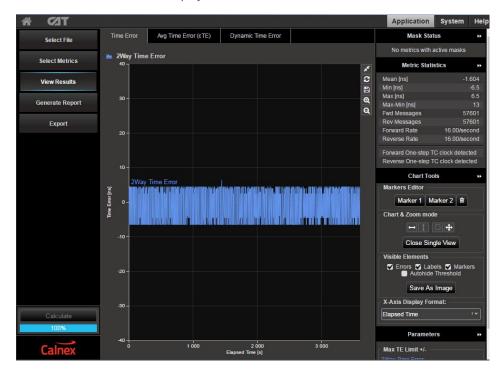

7. Select the *Time Error* tab to display the **raw unfiltered** Time Error results.

8. Click on the Select Metrics button, then select the 2Way Time Error metric only. This will display the following graph:

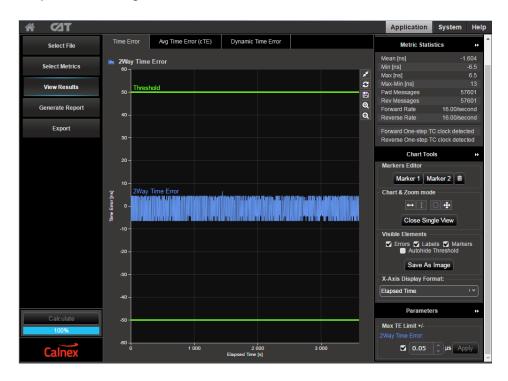

- 9. Set the MaxITEI limit to either 100ns for Class A devices or 70ns for Class B devices. This will change the Thresholds on the graph.

- 10. Compare the results against the thresholds.

### 5. Time Noise Tolerance - G.8273.3 Section 7.2

#### **Test Description**

This test checks whether the clock can maintain network limits at the output with maximum noise at the input.

#### **Measurement Process**

The standard recommends testing by stressing only the SyncE input. This is reflected in the test procedure detailed below.

Note: The Master/Slave Emulation Configuration steps described in Section 3 must be performed prior to this test.

#### **Test Procedure**

- 1. To enable SyncE ESMC Generation, select *Packet Generation* with **SSM code** of *QL\_PRC*.

- 2. To start ESMC generation press the **Start** button.

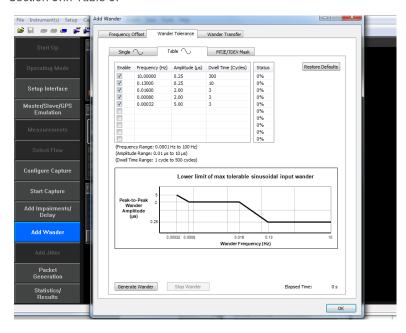

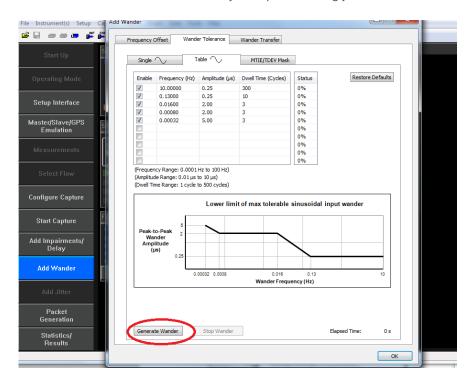

3. Select Add wander > Wander Tolerance > Table to apply sinusoidal wander to the SyncE input based on G.8262 Section 9.1.1 Table 9.

4. Select **Generate Wander** to stress the SyncE input accordingly.

- 5. Select to begin the measurement.

- 6. Once Wander Generation has finished and at least 1000s have passed, select Stop Capture to end the measurement.

### **Expected Outcome**

The Vendor DUT should maintain reference and not be subjected to switching reference or enter holdover state. This must be determined from the device itself (e.g. via the management interface).

# 6. Time Noise Transfer - G.8273.3 Clause 7.3

# **Test Description**

Measures how Time Error on the input is transferred to the output.

### **Measurement Process**

The Noise Transfer requirements for a T-TC device have not yet been finalised.

The test procedure will appear here once the Noise Transfer requirements are more fully defined.

# 7. Packet Layer Transient Response and Holdover Performance – G.8273.3 Clause 7.4

### 7.1. Test Description – Packet Layer Transient Response

The PTP to PTP transient response requirements applicable to a T-TC have not yet been defined.

The test procedure will appear here when such a definition is available.

# 7.2. Test Description – Holdover Performance

A T-TC does not support time holdover.

# Appendix 1 – Tests for a G.8273.3 T-TC

| Test                                                       | Objective                                                                                                                                                                                                                               | Test Method                                                                                                                                                         | Output Limit (PTP and 1pps) <sup>2</sup>                                                                    |  |         |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|---------|

| Time Error<br>Generation<br>(G.8273.3,<br>Clause 7.1)      | With stable input references, measure the inherent time error (MaxITEI, cTE and dTE) produced by the internal clock.                                                                                                                    | Apply a stable time reference to the PTP input.  Apply a stable frequency reference to the SyncE input.  Repeat without a SyncE reference <sup>3</sup> .            | MaxITEI:4  cTE:  dTE <sub>LF</sub> :5  dTE <sub>HF</sub> :6                                                 |  | Class B |

| Time Error<br>Tolerance<br>(G.8273.3,<br>Clause 7.2)       | Measures whether the clock can operate correctly with maximum noise input at the input.  The test must be carried out with noise on the SyncE input.  Clock under test should not:  generate alarms  switch reference  go into holdover | SyncE tolerance: Simultaneously apply sine wave phase wander to the SyncE input according to G.8262, Table 9. Repeat without a SyncE reference <sup>7</sup> .       | No output performance limit. Clock under test should not: generate alarms switch reference go into holdover |  |         |

| Time Error<br>Transfer<br>(G.8273.3,<br>Clause 7.3)        | Measures how time error on the input is transferred to the output.  SyncE-to-PTP transfer function: Upper cut-off from 1 to 10Hz                                                                                                        | SyncE to PTP:  Apply a stable time reference to the PTP input.  Apply a set of sine wave phase modulations of 200ns p-p amplitude at several different frequencies. | Tone frequencies and amplitudes                                                                             |  |         |

| Transients<br>and<br>Holdover<br>(G.8273.3,<br>Clause 7.4, | Measure the response to a SyncE rearrangement transient.  Measures the response to entry into holdover caused by loss of packets at PTP input.                                                                                          | No procedure defined yet.  A T-TC does not support Time holdover.                                                                                                   |                                                                                                             |  |         |

<sup>&</sup>lt;sup>2</sup> Same limits apply to 1pps and PTP outputs. It is assumed that the 1pps should track the PTP output closely, although there is no specification for how closely they should track.

<sup>&</sup>lt;sup>3</sup> G.8273.3 doesn't currently specify the performance in the absence of SyncE, therefore repeating the test without the use of SyncE input reference is optional.

$<sup>^4\,\</sup>mbox{Max}|\mbox{TE}|$  is calculated on the raw, unfiltered time error data.

$<sup>^{5}</sup>$  MTIE and TDEV are calculated after low-pass filtering by 0.1Hz. Same values apply to both Class A and Class B devices.

<sup>&</sup>lt;sup>6</sup> TIE is measured after high-pass filtering by 0.1Hz. Same values apply to both Class A and Class B devices.

Calnex Solutions Ltd Oracle Campus Linlithgow EH49 7LR United Kingdom

t: +44 (0) 1506 671 416 e: info@calnexsol.com

# calnexsol.com

$\hfill \odot$  Calnex Solutions, 2018. This information is subject to change without notice.

CX5021 v4.0 November 18